Decomposition Based Approach for the Synthesis of Threshold Logic Circuits

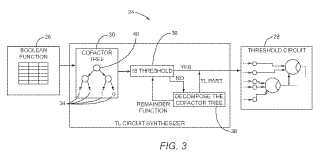

A computerized system and method for synthesizing threshold logic circuits is disclosed. The disclosed system and method receives a Boolean function and converts the Boolean function into a novel cofactor tree data structure like a BDD and an MML factor tree. Functions of the nodes making up the cofactor tree are tested to determine whether or not they are threshold. If is the function of a node is a threshold function, the process continues with the parent node. If the function of the node is not threshold, either the positive cofactor or negative cofactor of the node is decomposed. The cofactor tree data structure is also restructured to account for this process. The process then continues on the restructured cofactor tree data structure. The process terminates when the root node of the cofactor tree data structure is processed and the threshold circuit implementing the inputted Boolean function is outputted.Attached files:

Patents:

WO 2,010,048,206

Inventor(s): GOWDA TEJASWI [US]; VRUDHULA SARMA [US]

Type of Offer: Licensing

« More Computer Science Patents