SRAM cell with intrinsically high stability and low leakage

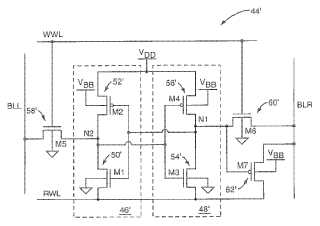

A Static Random Access Memory (SRAM) cell having high stability and low leakage is provided. The SRAM cell includes a pair of cross-coupled inverters providing differential storage of a data bit. Power to the SRAM cell is provided by a read word line (RWL) signal, which is also referred to herein as a read control signal. During read operations, the RWL signal is pulled to a voltage level that forces the SRAM cell to a full-voltage state. During standby, the RWL signal is pulled to a voltage level that forces the SRAM cell to a voltage collapsed state in order to reduce leakage current, or leakage power, of the SRAM cell. A read-transistor providing access to the bit stored by the SRAM cell is coupled to the SRAM cell via a gate of the read transistor, thereby decoupling the stability of the SRAM cell from the read operation.Attached files:

Patents:

US 7,920,409

Inventor(s): CLARK LAWRENCE T [US]; BADRUDDUZA SAYEED AHMED [US]

Type of Offer: Licensing

« More Computer Science Patents