Hybrid Group IV/III-V Semiconductor Structures

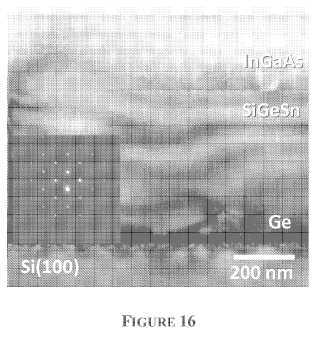

Described herein are semiconductor structures comprising (i) a Si substrate; (ii) a buffer region formed directly over the Si substrate, wherein the buffer region comprises (a) a Ge layer having a threading dislocation density below about 105 cm-2; or (b) a Ge1-xSnx layer formed directly over the Si substrate and a Ge1-x-ySixSny layer formed over the Ge1-xSnx layer; and (iii) a plurality of III -V active blocks formed over the buffer region, wherein the first III- V active block formed over the buffer region is lattice matched or pseudomorphically strained to the buffer region. Further, methods for forming the semiconductor structures are provided and novel Ge1-x-y SixSny, alloys are provided that are lattice matched or pseudomorphically strained to Ge and have tunable band gaps ranging from about 0.80 eV to about 1.4O eV.Attached files:

Patents:

WO 2,010,044,978 [MORE INFO]

Inventor(s): KOUVETAKIS JOHN [US]; MENENDEZ JOSE [US]

Type of Offer: Licensing

« More Electronics Patents