Methodology and apparatus for reduction of soft errors in logic circuits

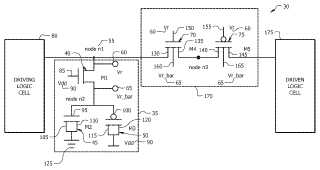

The present invention includes a circuit-level system and method for preventing the propagation of soft errors in logic cells. A radiation jammer circuit in accordance with the present invention, including an RC differentiator and a depletion mode MOS circuit, when inserted at the output of a logic cell, significantly reduces the propagation of transient glitches. The radiation jammer circuit is a novel transistor-level optimization technique, which has been used to reduce soft errors in a logic circuit. A method to insert radiation jammer cells on selective nodes in a logic circuit for low overheads in terms of delay, power, and area is also introduced.Attached files:

Patents:

US 7,804,320 issued 2010-09-28 [MORE INFO]

US 7,944,230 issued 2011-05-17 [MORE INFO]

Inventor(s): RANGANATHAN NAGARAJAN [US]; BHATTACHARYA KOUSTAV [US]

Type of Offer: Licensing

« More Engineering - Electrical Patents